圖3b. 每個延遲設置上信號幅度和SFDR性能的映射結果(放大)。

針對大量原始模擬帶寬的前端設計

首先,如果應用的關鍵目標是處理10 GHz的帶寬,我們顯然應考慮RF方式。請注意,ADC仍然是電壓型器件,不會考慮功率。這種情況下,"匹配"這個詞應該謹慎使用。我們發現,讓一個轉換器前端在每個頻率都與100 MSPS轉換器匹配幾乎是不可能的;高頻率帶寬的RF ADC不會有太大的不同,但挑戰依舊。術語"匹配"應表示在前端設計中能產生最佳結果的優化。這是一個無所不包的術語,其中,輸入阻抗、交流性能 (SNR/SFDR)、信號驅動強度或輸入驅動、帶寬以及通帶平坦度,這些指標都能產生該特定應用的最佳結果。

最終,這些參數共同定義了系統應用的匹配性能。開始寬帶前端設計時,布局可能是關鍵,同時應當最大限度地減少器件數量,以降低兩個相鄰IC之間的損耗。為了達到最佳性能,這兩方面均非常重要。將模擬輸入網絡連接在一起時務必小心。走線長度以及匹配是最重要的,還應盡量減少過孔數量,如圖4所示。

圖4. THA和ADC布局。

信號通過差分模式連接到THA輸入(我們同時是也提供單端射頻信號輸入的參考設計鏈路),形成單一前端網絡。為了最大限度地減少過孔數量和總長度,我們在這里特別小心,讓過孔不經過這兩條模擬輸入路徑,并且幫助抵消走線連接中的任何線腳。

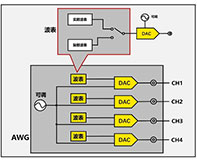

最終的設計相當簡單,只需要注意幾點,如圖5所示。所使用的0.01 F電容是寬帶類型,有助于在較寬頻率范圍內保持阻抗平坦。典型的成品型0.1 F電容無法提供平坦的阻抗響應,通常會在通帶平坦度響應中引起較多紋波。THA輸出端和ADC輸入端的5和10串聯電阻,有助于減少THA輸出的峰化,并最大限度地降低ADC自身內部采樣電容網絡的殘余電荷注入造成的失真。然而,這些值需要謹慎地選擇,否則會增加信號衰減并迫使THA提高驅動強度,或者設計可能無法利用ADC的全部量程。

最后討論差分分流端接。當將兩個或更多轉換器連接在一起時,這點至關重要。通常,輕型負載(例如輸入端有1 k負載)有助于保持線性并牽制混響頻率。分流器的120 分流負載也有此作用,但會產生更多實際負載,本例中為50 ,這正是THA希望看到并進行優化的負載。

圖5. THA和ADC前端網絡及信號鏈。

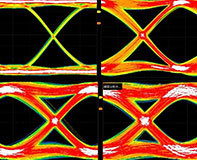

現在看結果!檢查圖6中的信噪比或SNR,可以看出在15 GHz范圍上可以實現8位的ENOB(有效位數)。這是相當不錯的,想想對于相同性能的13 GHz示波器,您可能支付了12萬美元。當頻率向L、S、C和X波段移動時,集成帶寬(即噪聲)和抖動限制開始變得顯著,因此我們看到性能出現滾降。

還應注意,為了保持THA和ADC之間的電平恒定,ADC的滿量程輸入通過SPI寄存器內部更改為1.0 V p-p。這有助于將THA保持在線性區域內,因為其最大輸出為1.0 V p-p差分。