電源噪聲是電磁干擾的一種,其傳導噪聲的頻譜大致為10kHz~30MHz,最高可達150MHz。電源噪聲,特別是瞬態(tài)噪聲干擾,其上升速度快、持續(xù)時間短、電壓振幅度高、隨機性強,對微機和數(shù)字電路易產(chǎn)生嚴重干擾。

示波器頻域分析在電源調(diào)試的應用

本文談到這么多年來最受關注的電源噪聲測量問題,有最實用的經(jīng)驗總結,有實測案例佐證,有仿真分析相結合。

在電源噪聲的分析過程中,比較經(jīng)典的方法是使用示波器觀察電源噪聲波形并測量其幅值,據(jù)此判斷電源噪聲的來源。但是隨著數(shù)字器件的電壓逐步降低、電流逐步升高,電源設計難度增大,需要使用更加有效的測試手段來評估電源噪聲。本文是使用頻域方法分析電源噪聲的一個案例,在觀察時域波形無法定位故障時,通過FFT(快速傅立葉變換)方法進行時頻轉(zhuǎn)換,將時域電源噪聲波形轉(zhuǎn)換到頻域進行分析。電路調(diào)試時,從時域和頻域兩個角度分別來查看信號特征,可以有效地加速調(diào)試進程。

在單板調(diào)試過程中發(fā)現(xiàn)一個網(wǎng)絡的電源噪聲達到80mv,已經(jīng)超過器件要求,為了保證器件能夠穩(wěn)定工作必須降低該電源噪聲。

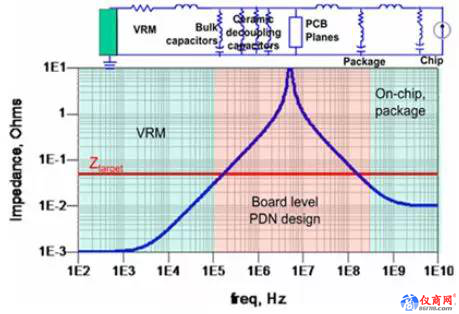

在調(diào)試該故障前先回顧下電源噪聲抑制的原理。如下圖所示,電源分配網(wǎng)絡中不同的頻段由不同的元件來抑制噪聲,去耦元件包含電源調(diào)整模塊(VRM)、去耦電容、PCB電源地平面對、器件封裝和芯片。VRM包含電源芯片及外圍的輸出電容,大約作用于DC到低頻段(100K左右),其等效模型是一個電阻和一個電感組成的二元件模型。去耦電容最好使用多個數(shù)量級容值的電容配合使用,充分覆蓋中頻段(數(shù)10K到100M左右)。由于布線電感和封裝電感的存在,即時大量堆砌去耦電容也難以在更高頻起到作用。PCB電源地平面對形成了一個平板電容,也具有去耦作用,大約作用在數(shù)十兆。芯片封裝和芯片負責高頻段(100M以上),目前的高端器件一般會在封裝上增加去耦電容,此時PCB上的去耦范圍可以降低到數(shù)十兆甚至幾兆。因此,在電流負載不變的情況下,我們只要判斷出電壓噪聲出現(xiàn)在哪個頻段,那么針對這個頻段所對應的去耦元件進行優(yōu)化即可。在兩個去耦元件的相鄰頻段時兩個去耦元件會配合作用,所以在分析去耦元件臨界點時相鄰頻段的去耦元件也要同時納入考慮。