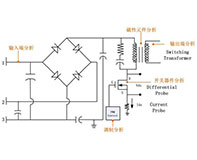

假設一個LDO系統在0dB時的截止頻率是30kHz。在其輸出端增加輸出電容為10uF,輸出電容的ESR=1ohm。則在16kHz處產生零點。

一般的LDO會由負載阻抗、輸出容抗等自身產生一些極點。圖中有3個極點(具體由來就不做分析,可由網絡分析儀掃描出),但有1個Ppwr在0dB之后的頻段,也就是帶寬之外,可以不考慮。從上面兩幅波特圖的對比看出,第二張圖增益曲線,當增加了輸出電容后,從80dB到0dB變得更平緩些。系統的帶寬大概從40KHz增加到100KHz左右。相位裕度也相應的增加(此例就不仔細計算了)。

那么系統對ESR又有什么要求呢?比如此例中設ESR=20ohm,則零點頻率會降低到Fzero=800Hz,使系統的帶寬增加到2MHz,從整個的波特圖我們發現在100K到2MHz之間又多了一個極點Ppwr。這就意味著系統又有了-90度的相移,零點就失去了其意義。那么ESR是不是越小越好呢?設ESR=50mohm。零點頻率會降到320kHz。不用看就知道,系統地穩定性基本沒改變,因為系統的帶寬就是40KHz,增加的零點頻率為320KHz已經超出了帶寬。

為了補償LDO穩壓器的。所以選擇的電容ESR要求要嚴格,首先要符合系統的回路頻率特性,同時也要有較好的溫度特性,不能隨溫度變化而變化過大。頻率響應也是重要的指標。這點鉭電容是比較好的選擇。(ESR是指在一定溫度下的某個頻率下的最大阻值,廠商一般定義為25攝氏度100KHz)