HIOKI日置科技新品發布了電壓偏置測試系統CN010,通過我司LCR測試儀、電壓偏置單元搭配定制的測試軟件,幫助半導體行業的用戶快速完成SiC、GaN、MLCC的偏壓測試,輕松把握半導體器件的直流偏置特性研究。

1、測試原理

C-V測量廣泛用于測量半導體參數,研發端的工程師往往采用C-V測量技術評估新材料、開發前的驗證評估工作,測試端的工程師會對一些被動元器件和功率器件、對供貨商的材料進行資格檢驗,檢測工藝參數。

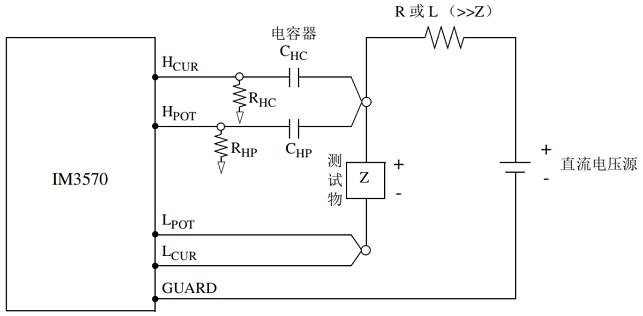

HIOKI日置C-V測試系統的回路結構圖如下所示,利用LCR表的四端子測試方法,將電壓源負端與LCR的GUARD端子相連,并由偏置單元施加到被測物兩端。通過交流信號注入法來獲取不同偏置電壓下的阻抗、相位、電容值、損耗因子等相關電參數,并通過PC軟件描繪出特性曲線。

直流電壓偏置電路

2、測試應用

應用①:薄膜電容MLCC(Multi-layor ceramic capacitor)

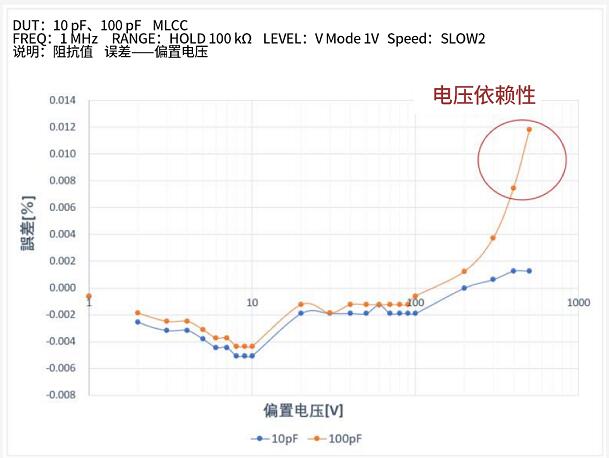

MLCC貼片電容自身的直流偏壓特性(DC Bias Characteristics)—— 在MLCC兩端施加直流電壓時,直流偏壓對極化機制的鉗制作用使偶極子的自由翻轉變得更加困難,相比未施加直流電壓時,電壓的升高使得其介電常數逐漸變小,導致在兩端直流電壓升高的過程中,電容值呈下降趨勢。

大容量的陶瓷電容的標稱容值隨著外部直流工作點的變化而明顯地變化(例如DCDC的輸出濾波電容等),故在設計電路時,是需要考慮和計算驗證的。

應用②:二極管結電容

結電容是二極管的一個寄生參數,由內部載流子的物理特性而形成的電容效應,可以看作是并聯在二極管上的等效電容。結電容分為勢壘電容與擴散電容構成。PN結外施加正偏電壓時,結電容主要是擴散電容,PN結施加反偏電壓時,結電容主要是勢壘電容。在高頻的電路設計中,往往要根據實際情況需要考慮結電容帶來的影響。

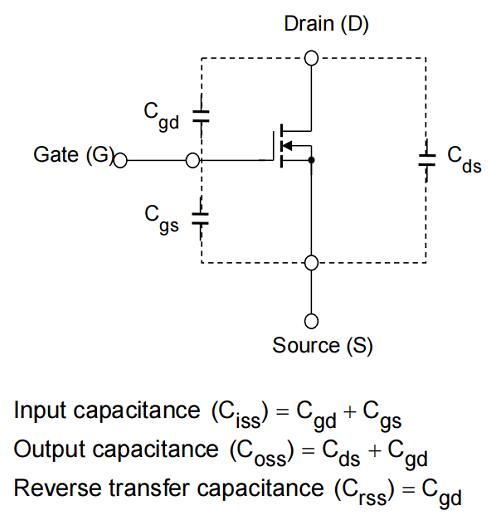

應用③:MOSFET的寄生電容&米勒效應

一般MOSFET的Datasheet中與寄生電容相關的參數為表中的Ciss、Coss、Crss,這三項是影響開關特性的重要參數,廠家將其分類到動態特性(Dynamic Characteristic)中,并標注相關測試條件供工程師參考。上述寄生電容對漏極-源極間電壓VDS具有依賴性,當VDS增加時,C值有下降的趨勢。HIOKI日置的C-V解決方案可以描繪出各寄生參數關于VDS的特性曲線。

下面簡單介紹MOSFET的一般動作過程:可以簡單的理解為驅動源對MOSFET的輸入電容(主要是柵源極電容Cgs)的充放電過程;當Cgs達到門檻電壓之后,MOS管逐漸導通。隨后Vds開始下降,Id開始爬升,MOS管進入飽和區。但由于米勒效應的存在,Vgs會持續一段時間不再上升,盡管Id已經達到峰值,Vds還在繼續下降,直到米勒電容充滿電,Vgs又回升到驅動電壓的值,此時Vds徹底歸零,開通結束。

以上的動態過程影響了MOS的動作時間、驅動能力和開關損耗等多方面特性,在驅動回路的設計中往往要對此進行評估和考量。

(圖1)電容等效電路

(圖2)電容與 VDS

圖片來源:https://toshiba-semicon-storage.com/cn/semiconductor/knowledge/faq/mosfet.html

3、系統構成