近日來,串擾測試話題熱度持續,各工程師都在尋找相關的串擾測試方案,前些時日,中星聯華科(北京)有限公司發布了《【有料干貨】串擾測試方案(上篇)》,許多工程師紛紛留言期待下篇。

現在,下篇終于來了,快來看看中星聯華科技(北京)有限公司給我們帶來了什么樣的串擾測試方案吧。

首先,我們先來看看上篇內容:【有料干貨】串擾測試方案(上篇)

2.>>>串擾的危害<<<

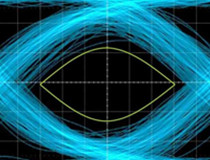

當耦合信號或串擾信號足夠大時,接收串擾信號的信號線上就會出現信號完整性問題。串擾可能在受害線上引起尖峰脈沖,也能引起電路時延的改變。串擾會引起系統的不穩定,嚴重時甚至可能會引起系統的崩潰。下圖是高速傳輸鏈路不同的位置的眼圖測量。

在PCB設計中,如果處理不當,串擾對PCB的信號完整性將產生以下兩種典型的影響。

由串擾引起的數字電路功能錯誤是電路設計中最為常見的一種。

串擾噪聲導致電平邏輯錯誤

2.2串擾引起的時序延時

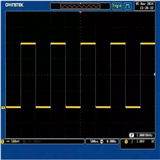

在數字系統設計中,時序問題是一個必須考慮的重要問題。下圖顯示了由串擾噪聲引起的時序問題。圖中下半部分是干擾線產生的噪聲脈沖,當噪聲脈沖疊加到被干擾信號上,就會造成被干擾網絡信號傳輸延時減少。盡管這種減少網絡傳輸延時的串擾噪聲對改善 PCB 時序是有幫助的,但在實際 PCB設計中,由于干擾信號的不確定性,這種延時是無法控制的,因而對這種串擾對于電路設計造成嚴重的干擾,是需要避免的。

串擾噪聲導致的信號傳輸延時

3.>>>串擾測量<<

以往人們通常把印刷電路板、連接器、電纜和過孔當成是簡單的部件,稍加考慮或者無需其他因素就可以很容易地把它們組成一個系統。現在,從邏輯電平0到邏輯電平1的數據上升時間30ps,如此高速的信號在傳輸線路上傳輸時會形成微波傳輸線效應,這些傳輸線效應對信號的影響會更加復雜。為了保證信號傳輸的質量,串擾測試成為了研發生產中不可缺少的環節。

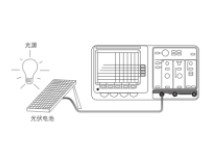

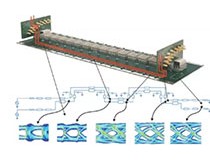

下圖是一個針對串擾測試全面的方案設計圖,能夠支持串擾測試、眼圖測試、誤碼測試、及阻抗測試。這里著重介紹串擾測試部分。

總體方案設計

中星聯華科技(北京)有限公司的SL3000A插卡式高速串行誤碼儀能夠通過可插拔模塊同時具有串擾源產生、數據源產生、誤碼檢測及比對等功能。

本系統特點:

1.支持NRZ/PAM4波形;

2.單通道碼速率1-32GBd連續可調,支持生級至56GBd;

3. 支持同步/異步串擾;

3.上升下降時間:15ps(20%-80%)@28Gbps;

4.輸出幅度:0.1Vpp-1Vpp,選件擴展最大幅度到4Vpp,選件擴展為直流輸出,偏置電壓-4V至+4V可調;

5.支持偽隨機碼型:PRBS7/9/10/13/15/23/31/64bit UDP;

6.觸發時鐘輸出支持碼速率2/4/8/16分頻比可調;

8.支持內部精準時基,頻率穩定度≤±0.05ppm,支持內外時基自動切換;

9.可以調節頻率精度至±0.1ppm。